Since “software ate the world,” most engineers and engineering students I meet are focused on software, and even more specifically application software. However, designing the hardware can be as exciting as software.

So, how does one design hardware? One might think of it as a process closer to mechanical or civil design. Maybe you open up a CAD software and start drawing. Although this is possible for designing PCBs, it would be insane to try drawing a system with billions of transistors. The engineering community noticed this early on. So, the first hardware description languages were introduced. Although there is work being done on HDLs since the 60s, the most well-known languages, VHDL and Verilog, were introduced in early 1980s. These languages help engineers to define the behaviour of the hardware in code. Then, this code is synthesised into a drawing that can be printed on silicon wafers in a fab.

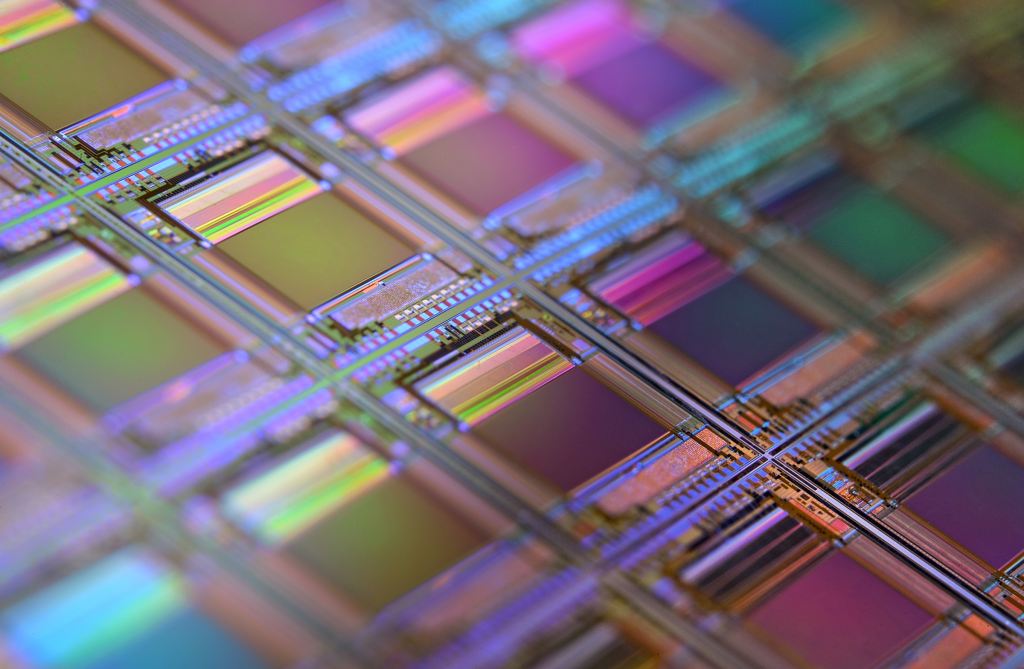

So, how does one use a hardware description language to design hardware? Let’s learn this through some examples we will write in Verilog. First of all, I want to show you an integrated circuit I have at home. This is a part I quickly build for a project and It includes this IC chip that is a bunch of NOT gates. They simply reverse a digital signal from 0 to 1 or from 1 to 0. This particular device has four inputs and four outputs such that the signal at the first input decides the first output and so on. Let’s try to model this circuit in Verilog.

The first thing we put into our file is a module. A module is a part of hardware that has inputs, outputs and logic.

module some_not (input wire in, output wire out);

endmoduleHere we have a module with one input and one output. Inside the module, we describe the logic. Since we want to design a NOT gate, it is very easy. A NOT gate is very common, so it is already defined in Verilog.

module some_not (input wire in, output wire out);

not(out, in);

endmodule

Actually most logic gates you might know from a maths or computer science course are defined. These include AND, OR, NAND, XOR and so on. If we design our logic using these gates defined in Verilog, we are doing “gate level modelling.”

Another, and much more common, way to design hardware in Verilog is “behavioural modelling.” In this model, we define the logic by some kind of algorithm. A common way to define a not gate’s behaviour would be like this:

module some_not (input wire in, output wire out);

assign out = !in;

endmodule

A programmer would realise this is similar to how some programming languages work with booleans. One might even go ahead and design the same hardware like this:

module some_not (input wire in, output reg out);

always @* begin

if (in)

out = 0;

else

out = 1;

end

endmodule

Now, let’s design this integrated circuit with four inputs and outputs. While doing so, I want to tell a few more things about modules. Modules are the building blocks of a hardware design. We build larger modules by connecting modules and adding additional logic. Moreover, we can reuse a module description to put the logic in the module to multiple parts of the design.

module four_not (input wire in1, input wire in2, input wire in3, input wire in4,

output wire out1, output wire out2, output wire out3, output wire out4);

some_not first(in1, out1);

some_not second(in2, out2);

some_not third(in3, out3);

some_not fourth(in4, out4);

endmodule

Lastly, Verilog actually allows us to design this whole IC by writing one line in a module. An input or output in Verilog can be multiple bits. This code defines it so that out[i] = !in[i]

module four_not (input wire [3:0] in, output wire [3:0] out);

assign out = !in;

endmodule

If we synthesize all the models from these examples, we can see that all these models we designed generate the same hardware.

In today’s world, HDLs are widely used. Custom chips are becoming more common. The new AI software needs more and more hardware acceleration. It is an exciting time to do hardware design!

References

Photo by Laura Ockel on Unsplash

Leave a comment